# ECE 3411 Microprocessor Application Lab: Fall 2015

Quiz VII

There are  $\underline{3}$  questions in this quiz. There are  $\underline{9}$  pages in this quiz booklet. Answer each question according to the instructions given.

You have 45 minutes to answer the questions.

Some questions are harder than others and some questions earn more points than others—you may want to skim all questions before starting.

If you find a question ambiguous, be sure to write down any assumptions you make. **Be neat and legible.** If we can't understand your answer, we can't give you credit!

Write your name in the space below. Write your initials at the bottom of each page.

### THIS IS A CLOSED BOOK, CLOSED NOTES QUIZ. PLEASE TURN YOUR NETWORK DEVICES OFF.

Any form of communication with other students is considered cheating and will merit an F as final grade in the course.

Do not write in the boxes below

| 2 (x/30) | 3 (x/40) | <b>Total</b> (xx/100) |

|----------|----------|-----------------------|

|          |          |                       |

|          |          |                       |

|          | 2 (x/30) | 2 (x/30) 3 (x/40)     |

| N  | ame: |  |

|----|------|--|

| Τ. | am.  |  |

**Student ID:**

- 1. [30 points]: Answer the following questions:

- **a.** What do you understand by the term **Task's Execution Context**? List the four major components of a task's execution context for an AVR processor.

**b.** Briefly explain the terms **Preemption** and **Context Switching** in the context of RTOS.

**c.** Briefly explain the terms **Priority Inversion** and **Priority Inheritance** in the context of RTOS.

**d.** How does CAN protocol handle the bus arbitration when two devices want to transmit at the same time?

#### **2.** [30 points]: Consider the following while loop in the main code:

```

/* If not already equal to 0, task1_timer and task2_timer

are decremented every 1 millisecond in a timer ISR */

// Initializing. task1 is ready to execute

task1_timer = 0;

task2_timer = 0;

// Initializing. task2 is ready to execute

while (1)

{

if (task1_timer == 0) // if task1 is ready to run.

task1\_timer = t1;

task1();

// task1 takes m1 milliseconds to execute.

}

if (task2_timer == 0) // if task2 is ready to run.

{

task2_timer = t2;

task2();

// task2 takes m2 milliseconds to execute.

}

}

```

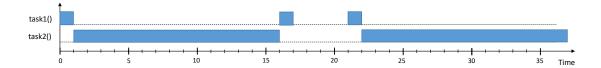

Suppose if t1=5, m1=1 and t2=20, m2=15 then the corresponding execution pattern is shown below:

Here task1() executes for 1 ms, task2() executes for 15 ms, and the MCU is idle for 4 ms. The same pattern starts getting repeated over and over.

In this example pattern, task2() is executed once per 21 ms (a frequency of 1/(21 ms)) and task1() is executed on average two times per 21 ms (an average frequency of 2/(21 ms)).

Similar to the above mentioned example, answer the following questions.

### **A.** Suppose t1=5, m1=1, t2=10, and m2=15.

Draw the execution pattern of the two tasks.

What is the frequency f1 in Hz at which task1() is called?

What is the frequency f2 in Hz at which task2() is called?

### **B.** Suppose t1=20, m1=1, t2=10, and m2=15. Draw the execution pattern of the two tasks.

What is the frequency f1 in Hz at which task1() is called?

What is the average frequency f2 in Hz at which task2() is called?

- **3. [40 points]:** You need to design an AVR-based system that includes four external devices in its address space:

- One SRAM of size 32 kilobytes, for data storage, with the following control signals:

- $\overline{WE}$ : Write Enable (Active Low).

- $\overline{OE}$ : Output Enable (Active Low).

- $\overline{CE}$ : Chip Enable (Active Low).

- Three 8-bit latches to drive digital outputs for 24 LEDs.

- LE: Latch Enable (Active High).

- $\overline{OE}$ : Output Enable (Active Low).

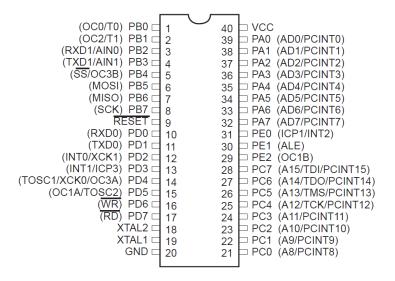

The system should be based on a MCU of the type Atmel AVR ATmega162 (shown in Figure 1).

Figure 1: ATmega162 Pin Configuration.

By completing the subsections A and B, design an interface between the ATmega162 and the external devices needed for this system.

#### A. Address Mapping & Decoding: (20 points)

Explain how you will organize the address space of the system and its associated decoding logic (remember that the lower 1280 addresses are reserved).

Show your calculations/methodology and design the address decoding logic.

#### **B.** Overall System Interconnects: (20 points)

Draw a detailed schematic of the system which shows the interconnection of components/chips (details may be limited to main signal lines/paths). Specify and draw chips, circuits and signals that you may find necessary to include.

## End of Quiz

Please double check that you wrote your name on the front of the quiz.

**Initials:**