ECE3411 – Fall 2015 Wrap Up

#### **Review Session**

#### Marten van Dijk, Syed Kamran Haider

Department of Electrical & Computer Engineering University of Connecticut Email: {vandijk, syed.haider}@engr.uconn.edu

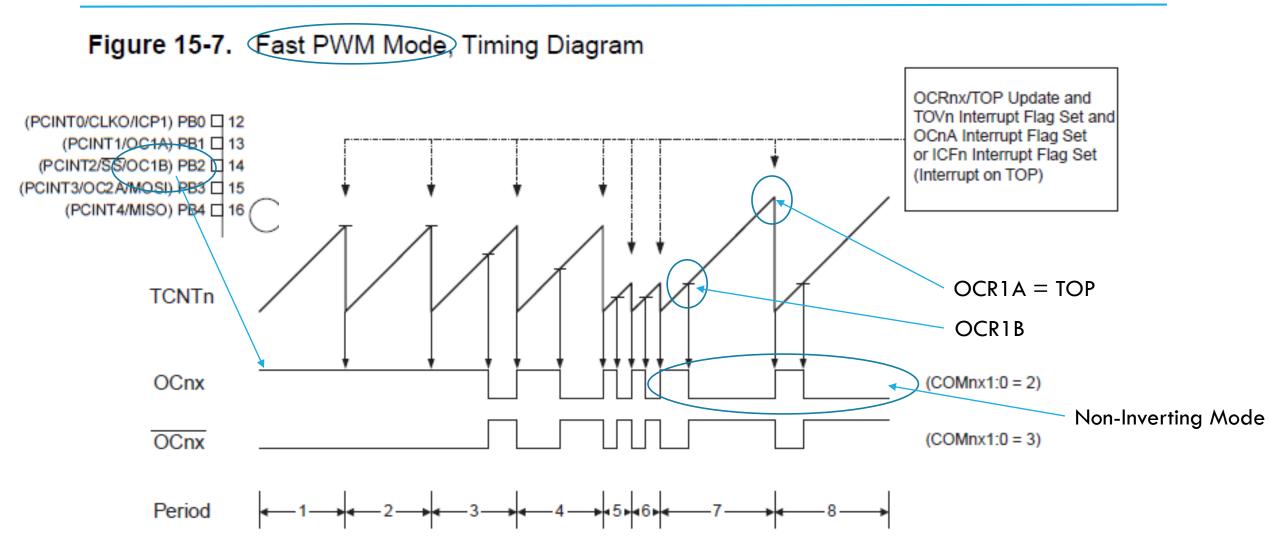

#### Pulse Width Modulation using Timer 1

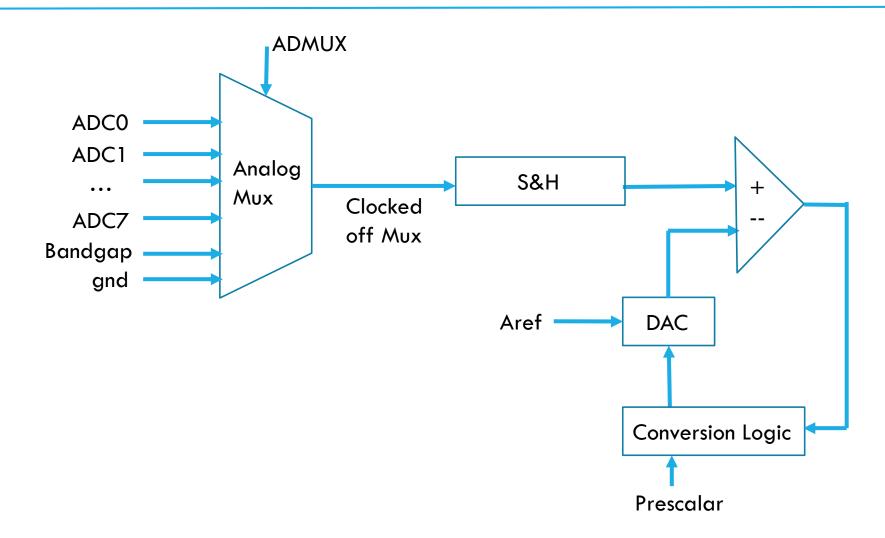

ADC

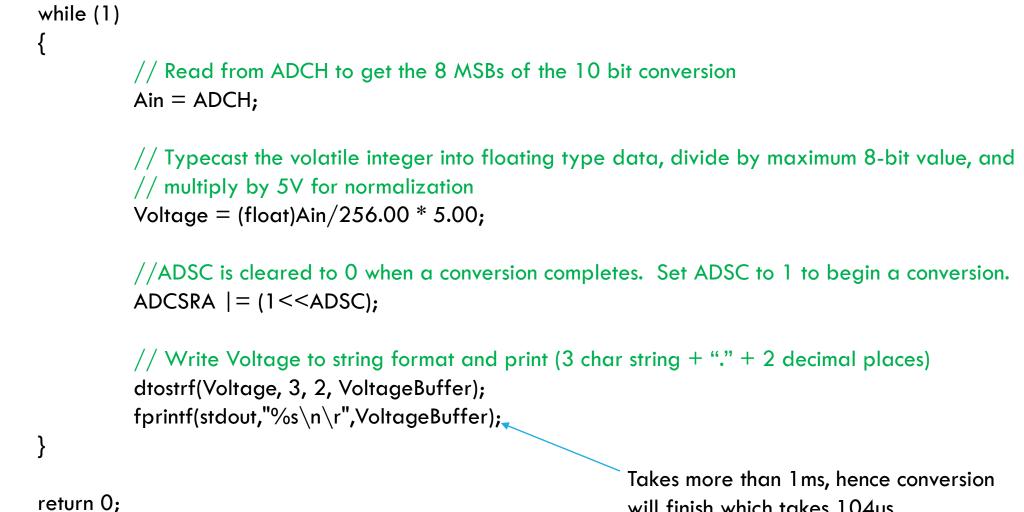

#### Example code ADC, no interrupt

void main(void)

DDRC &=  $0 \times 00$ ; // PC1 = ADC1 is set as input

uart\_init(); stdout = stdin = stderr = &uart\_str;

// ADLAR set to  $1 \rightarrow$  left adjusted result in ADCH // MUX3:0 set to 0001  $\rightarrow$  input voltage at ADC1 ADMUX = (1<<MUX0) | (1<<ADLAR);

// ADEN set to 1 → enables the ADC circuitry

// ADPS2:0 set to 111 → prescalar set to 128 (104us per conversion)

ADCSRA = (1<<ADEN) | (1<<ADPS2) | (1<<ADPS1) | (1<<ADPS0);</pre>

```

// Start A to D conversion

ADCSRA |= (1<<ADSC);

fprintf(stdout,"\n\rStarting ADC demo...\n\r");</pre>

```

Takes more than 1ms, hence conversion will finish which takes 104us

### Example code ADC, no interrupt

will finish which takes 104us

5

#### **ADC Noise Reduction**

#### 9.11.1 SMCR – Sleep Mode Control Register

The Sleep Mode Control Register contains control bits for power management.

| Bit           | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |      |

|---------------|---|---|---|---|-----|-----|-----|-----|------|

| 0x33 (0x53)   | - | - | - | - | SM2 | SM1 | SM0 | SE  | SMCR |

| Read/Write    | R | R | R | R | R/W | R/W | R/W | R/W | -    |

| Initial Value | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |      |

#### Table 9-2. Sleep Mode Select

| SM2 | SM1 | SM0 | Sleep Mode                      |  |

|-----|-----|-----|---------------------------------|--|

| 0   | 0   | 0   | Idle                            |  |

| 0   | 0   | 1   | ADC Noise Reduction             |  |

| 0   | 1   | 0   | Power-down                      |  |

| 0   | 1   | 1   | Power-save                      |  |

| 1   | 0   | 0   | Reserved                        |  |

| 1   | 0   | 1   | Reserved                        |  |

| 1   | 1   | 0   | Standby <sup>(1)</sup>          |  |

| 1   | 1   | 1   | External Standby <sup>(1)</sup> |  |

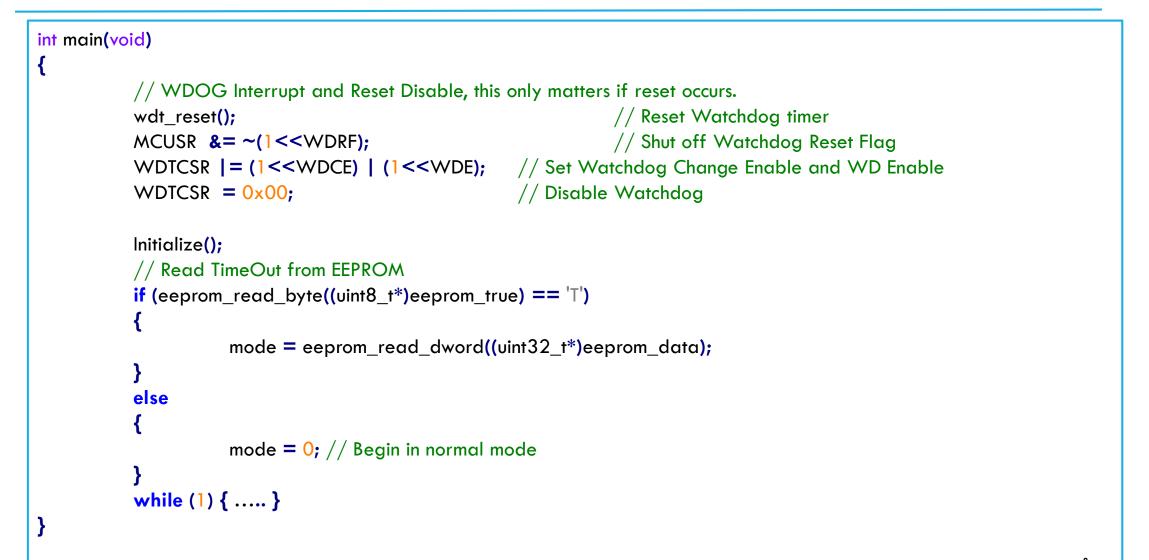

# Watchdog Timer

```

#include <avr/wdt.h>

#include <avr/eeprom.h>

#define eeprom_true 0 //Suppose you want to store a flag at position 0

#define eeprom_data 1 //Suppose you want to store data at position 1

ISR (WDT vect)

eeprom_write_dword((uint32_t*)eeprom_data,mode);

//Write our current mode to EEPROM

//Set write flag TRUE

eeprom_write_byte((uint8_t*)eeprom_true, 'T');

void Initialize(void)

... all other initialization ...

WDTCSR |= (1<<WDCE) | (1<<WDE); // Set Watchdog Condition Edit for four cycles

WDTCSR = (1 << WDE) | (1 << WDE) | (1 << WDP3); // Set WDT Int and Reset; Prescalar at 4.0s.

```

# Watchdog Timer

## What is an Interrupt (recap)?

- A HW signal that initiates and event

- Upon receipt of an interrupt, the processor

- Completes the instruction being executed

- Saves the program counter (so as to return to the same execution point)

- Loads the program counter with the location of the interrupt handler code (ISR)

- Executes the interrupt handler (ISR)

- In practice, real time systems can handle several interrupts in priority fashion

- Interrupts can be enabled/disabled (By setting appropriate registers.)

- Highest priority interrupts serviced first (Which ones have the highest priority in Atmega328P?)

- Processor must check for interrupts very frequently: If any have arrived, it stops immediately and runs the associated ISR

- Processor repeats: do one operation; check interrupts; if interrupts then suspend task and run ISR

## ISR

- ISR is a program run in response to an interrupt

- Disables all interrupts

- Clears the interrupt flag that got it called

- Runs code to service the event

- Re-enables interrupts

- Exits so the processor can go back to its running task

- Should be as fast as possible, because nothing else can happen when an interrupt is being serviced (when interrupts happen very frequently, tasks are being stalled and progress very slowly, in the worst case one instruction per ISR)

- Interrupts can be

- Prioritized (service some interrupts before others)

- Disabed (processor doesn't check or ignores all of them)

- Masked (processor only sees some interrupts)

# Scheduling Policies

Static Scheduling Schemes

- Round-robin scheduling

- Rate-monotonic scheduling

- Deadline-monotonic scheduling

- Shortest Remaining Time First

Dynamic Scheduling Schemes

- Earliest deadline first scheduling

- Least slack time scheduling

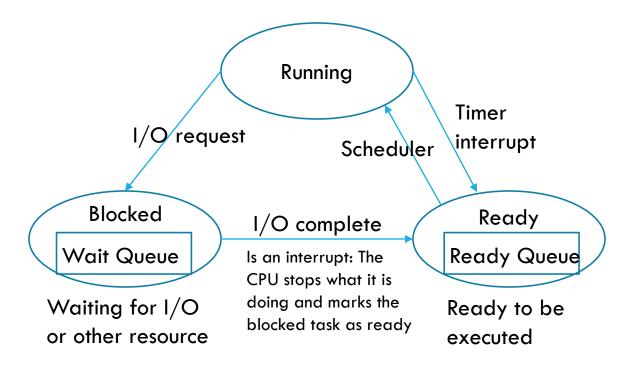

## Task State Diagram

- A task/process goes through several states during its life in a multitasking system

- Tasks are moved from one state to another in response to the stimuli marked on the arrows

- Any tasks that are ready to run sit on the ready queue. This queue may be prioritized so the most important task runs next.

- When the scheduler decides the current task has had enough time on the CPU, either because it finished or its time slice is up, the *Running* task is moved to the ready queue. Then the first task on the ready queue is selected for Running.

- If the Running task needs I/O or needs a resource that is currently unavailable, it is put on the blocked queue.

When its resource becomes available, it goes back to Ready.

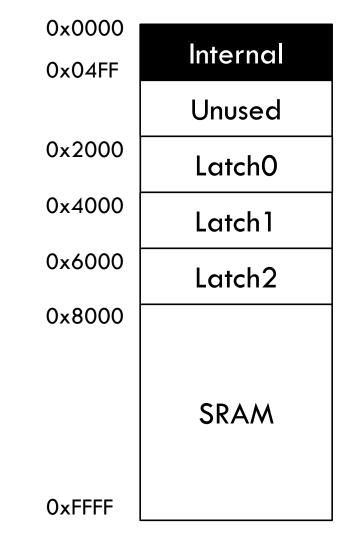

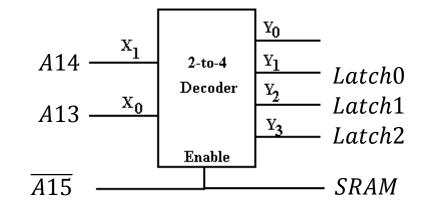

#### Address Decoding of selected Memory Map

| Device          | Address Range   | A15 A0              |

|-----------------|-----------------|---------------------|

| Internal/Unused | 0x0000 – 0x1FFF | 000x xxxx xxxx xxxx |

| Latch0          | 0x2000 – 0x3FFF | 001x xxxx xxxx xxxx |

| Latch 1         | 0x4000 – 0x5FFF | 010x xxxx xxxx xxxx |

| Latch2          | 0x6000 – 0x7FFF | 011x xxxx xxxx xxxx |

| SRAM            | 0x8000 – 0xFFFF | 1xxx xxxx xxxx xxxx |

# Bus Multiplexing & Address Decoding

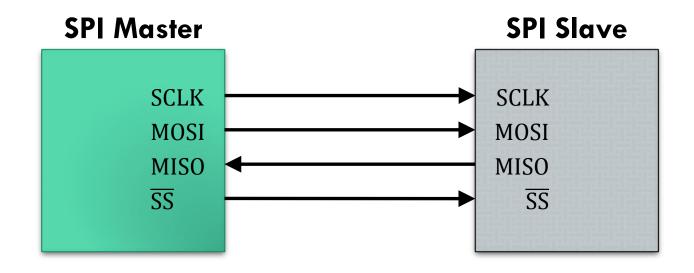

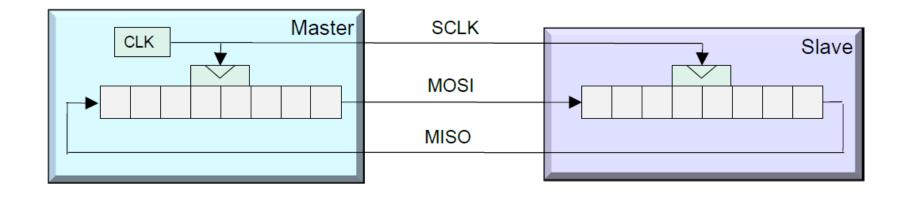

#### SPI: Serial Peripheral Interface

- Synchronous Data Transfer

- Master/Slave configuration

- 4-Line Bus

- Full Duplex operation

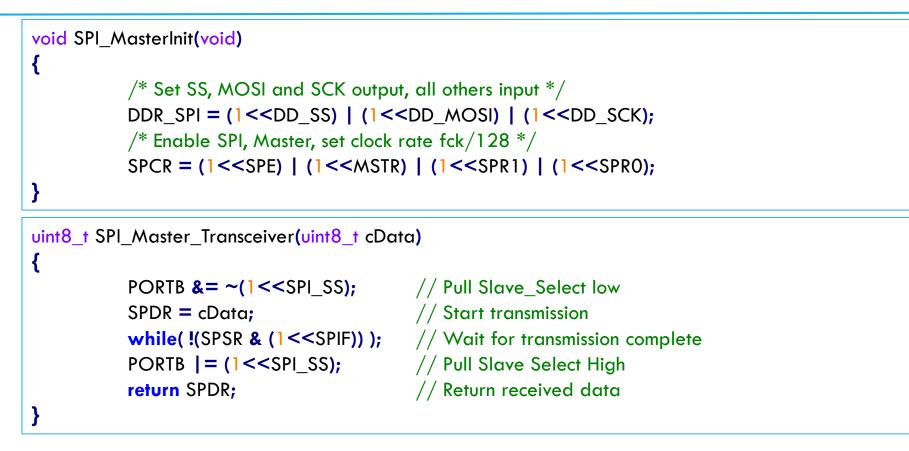

### SPI Master Example

#### Note:

DDR\_SPI in the examples must be replaced by the actual Data Direction Register controlling the SPI pins. DD\_SS, DD\_MOSI, DD\_MISO and DD\_SCK must be replaced by the actual data direction bits for these pins. E.g. if MOSI is placed on pin PB3, replace DD\_MOSI with DDB3 and DDR\_SPI with DDRB. SPI\_SS should be replaced with actual bit position of SS pin in the port corresponding to SPI pins.

### SPI Slave Example

```

void SPI SlaveInit(void)

٤

/* Set MISO output, all others input */

DDR SPI = (1 < <DD MISO);

/* Enable SPI */

SPCR = (1 < < SPE);

uint8 t SPI SlaveReceive(void)

l

/* Wait for reception complete */

while(!(SPSR & (1<<SPIF)));</pre>

/* Return Data Register */

return SPDR;

```

#### Note:

DDR\_SPI in the examples must be replaced by the actual Data Direction Register controlling the SPI pins. DD\_MOSI, DD\_MISO and DD\_SCK must be replaced by the actual data direction bits for these pins. E.g. if MOSI is placed on pin PB5, replace DD\_MOSI with DDB5 and DDR\_SPI with DDRB.

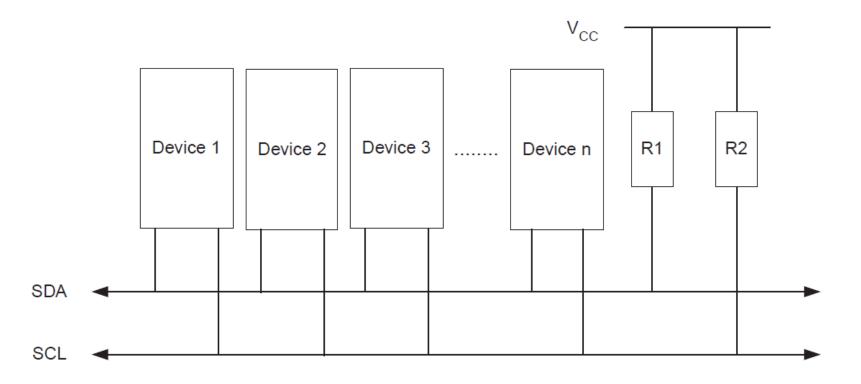

# I<sup>2</sup>C: Inter Integrated Circuit bus

- Also known as Two Wire Interface (TWI)

- Allows up to 128 different devices to be connected using only two bi-directional bus lines, one for clock (SCL) and one for data (SDA).

- All devices connected to the bus have individual addresses.

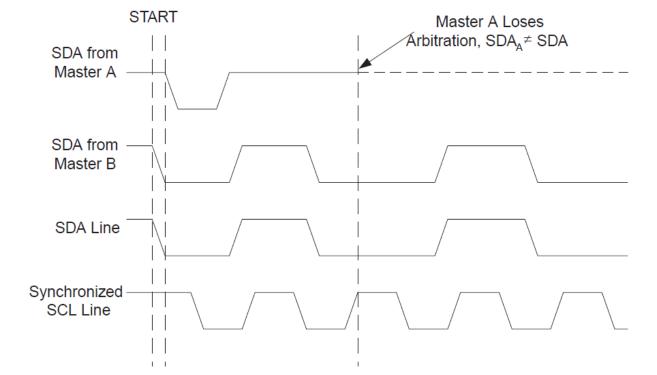

## **I<sup>2</sup>C Bus Arbitration**

- Arbitration is carried out by all masters continuously monitoring the SDA line after outputting data.

- If the value read from the SDA line does not match the value the Master had output, it has lost the arbitration.

Figure 21-8. Arbitration Between Two Masters