ECE3411 – Fall 2015 Lecture 2a.

#### UART: Universal Asynchronous Receiver & Transmitter

#### Marten van Dijk, Syed Kamran Haider

Department of Electrical & Computer Engineering University of Connecticut Email: {vandijk, syed.haider}@engr.uconn.edu

Based on the Atmega328P datasheet and material from Bruce Land's video lectures at Cornel

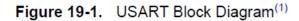

# USARTO (Ch. 19 ATmega328P Datasheet)

- USART = Universal Synchronous and Asynchronous serial Receiver and Transmitter

- Clock generator, Transmitter, Receiver

- Bolted on to the MCU

## USART

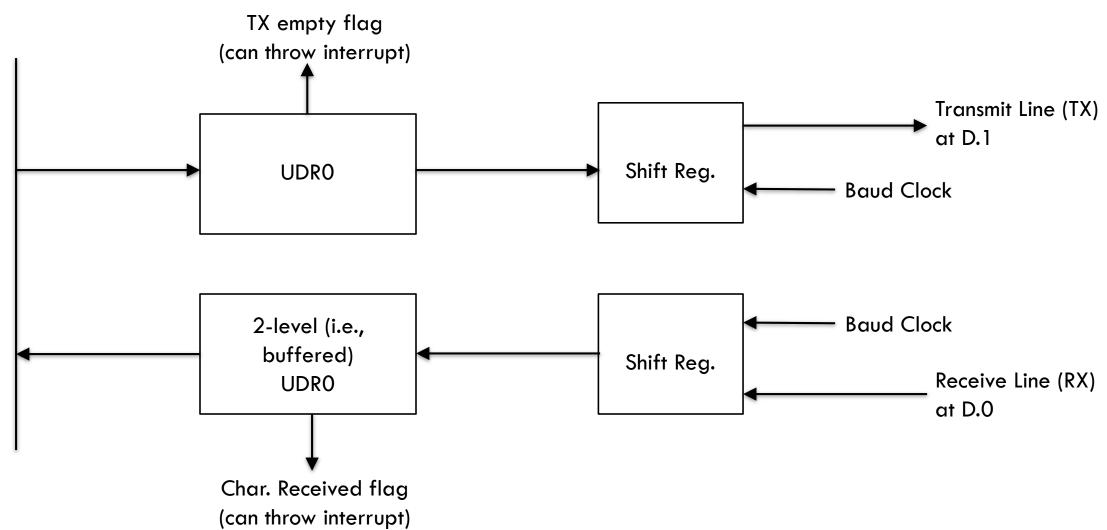

### TX and RX at PORTD

## USART

- USART communicates over a 3-wire cable: TX, RX, Gnd

- Designed for a mechanical printer, a long time ago; protocol is slow

- HW allows full-duplex, i.e., HW can transmit and receive at exactly the same time

- Need interrupt to utilize this in SW

- Baud rate in bits per second: 9600 Bd is approximately 0.1ms per bit

- This is slow: Therefore, in SW start transmitting a character, then do something else!

- In theory the Baud rate can be very large (1Mbit per second) but this can only be realized between MCUs

- The used cable limits the maximum possible Baud rate

- Per bit the receiving clock makes 4 measurements and they all need to match: All, e.g. 10, bits within a frame give 40 measurements that all need to match

- The Baud rates of the receiving and transmitting devices need to match within 1/40 = 2.5%

### **UBRROH** and **UBRROL**

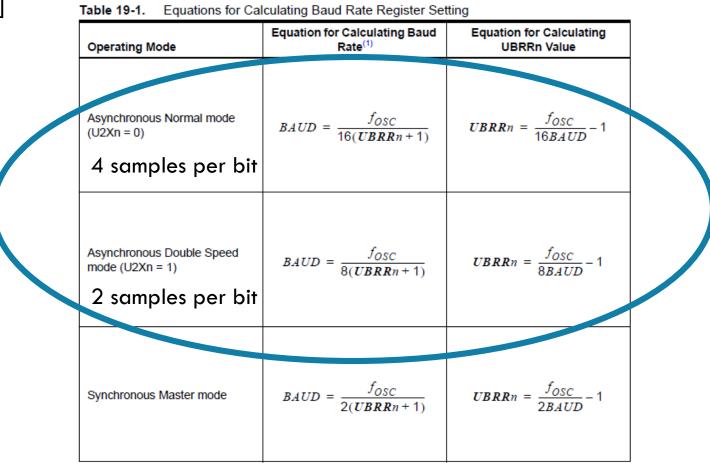

Baud rate is translated relative to the system oscillator clock frequency f\_OSC to two registers UBRROH and UBRROL, the high and low value of UBRRO which is in the range [0,4095] Table 19-1. Equations for Calculating Baud Rate Register Setting

6

#### **UBRROH and UBRROL**

#### 19.10.5 UBRRnL and UBRRnH – USART Baud Rate Registers

| Bit           | 15  | 14  | 13  | 12   | 11      | 10   | 9       | 8   |        |

|---------------|-----|-----|-----|------|---------|------|---------|-----|--------|

|               |     | _   | _   | _    |         | UBRR | n[11:8] |     | UBRRnH |

|               |     |     |     | UBRR | Rn[7:0] |      |         |     | UBRRnL |

|               | 7   | 6   | 5   | 4    | 3       | 2    | 1       | 0   |        |

| Read/Write    | R   | R   | R   | R    | R/W     | R/W  | R/W     | R/W |        |

|               | R/W | R/W | R/W | R/W  | R/W     | R/W  | R/W     | R/W |        |

| Initial Value | 0   | 0   | 0   | 0    | 0       | 0    | 0       | 0   |        |

|               | 0   | 0   | 0   | 0    | 0       | 0    | 0       | 0   |        |

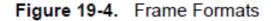

#### Frame Format

To transmit a byte (i.e., one char) we need at least one start bit (receiving clock starts when falling edge is received), 8 data bits, and one stop bit: Total of 10 bits.

- St Start bit, always low.

- (n) Data bits (0 to 8).

- P Parity bit. Can be odd or even.

- Sp Stop bit, always high.

- IDLE No transfers on the communication line (RxDn or TxDn). An IDLE line must be high.

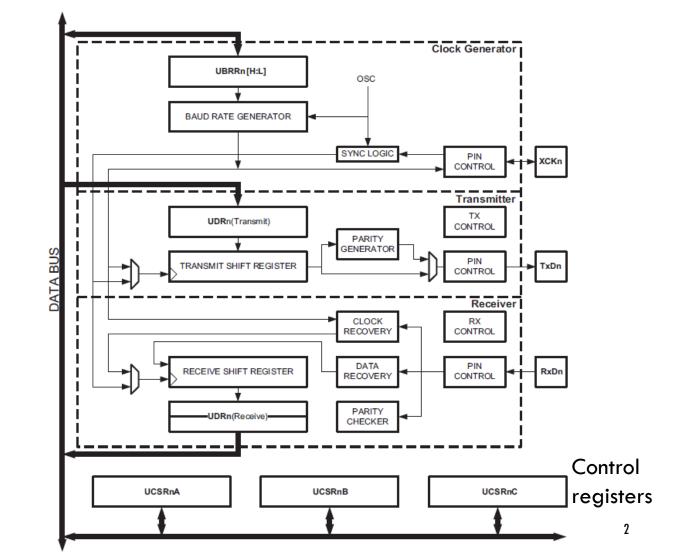

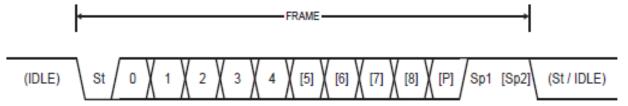

## UDRO for Transmission and Receiving

#### 19.10.1 UDRn – USART I/O Data Register n

The USART Transmit Data Buffer Register and USART Receive Data Buffer Registers share the same I/O address referred to as USART Data Register or UDRn. The Transmit Data Buffer Register (TXB) will be the destination for data written to the UDRn Register location. Reading the UDRn Register location will return the contents of the Receive Data Buffer Register (RXB).

(The receive and transmit buffers RXB and TXB are different in HW; in SW their names, i.e. I/O addresses, are the same. The shared name UDRO in read mode means that RXB is read, and UDRO in write mode means that TXB is written. Notice that reading and writing of bits in UDRO can be done simultaneously since they affect different hardware buffers!)

## **Control register: UCROA**

#### 19.10.2 UCSRnA – USART Control and Status Register n A

| Bit           | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0     | _      |

|---------------|------|------|-------|-----|------|------|------|-------|--------|

|               | RXCn | TXCn | UDREn | FEn | DORn | UPEn | U2Xn | MPCMn | UCSRnA |

| Read/Write    | R    | R/W  | R     | R   | R    | R    | RW   | R/W   |        |

| Initial Value | 0    | 0    | 1     | 0   | 0    | 0    | 0    | 0     |        |

- RXCO: Receive character complete  $\rightarrow$  There is something in the receive register worth reading

- TXCO: Transmit character compare → Is set when both entries in the Transmit Shift Register and Transmit Buffer (UDRO) are shifted out → Not very useful

- UDREO: Transmit data empty → Goes high when 1 of the two buffers (see above) is empty → Time to refill

- FEO: Frame error if 4 samples of a bit do not match  $\rightarrow$  Detects bad clock rate

- DOR0: Data overrun: If a new character is complete and RXC0 is still set, implies a lost char → SW did not read often enough

## **Control register: UCROA**

#### 19.10.2 UCSRnA – USART Control and Status Register n A

| Bit           | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0     |        |

|---------------|------|------|-------|-----|------|------|------|-------|--------|

|               | RXCn | TXCn | UDREn | FEn | DORn | UPEn | U2Xn | MPCMn | UCSRnA |

| Read/Write    | R    | R/W  | R     | R   | R    | R    | R/W  | R/W   | -      |

| Initial Value | 0    | 0    | 1     | 0   | 0    | 0    | 0    | 0     |        |

- UPEO: Parity error

- U2X0: Double speed (twice the baud rate)  $\rightarrow$  reduces error checking (only 2 samples per bit)

- MPCMO: Multiple processor address mode (can connect more than 2 devices to the line)

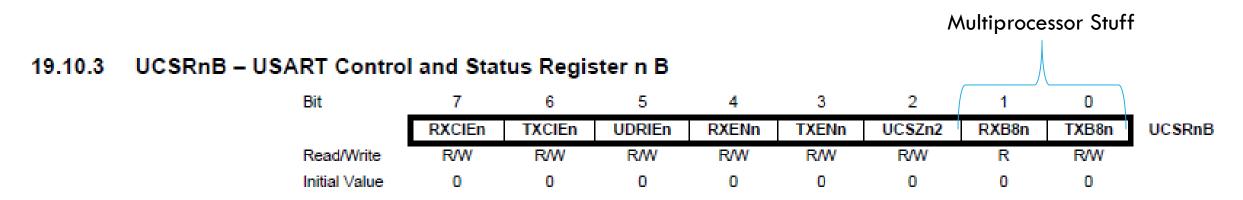

## Control register: UCSROB

- RXCIEO: Receive character complete interrupt enable ightarrow You can write an ISR for this

- TXCIEO: Enables interrupt for both members in TX queue being empty

- UDRIEO: Enables interrupt if the first of the output pipeline is empty

- RXENO: RX enable  $\rightarrow$  Disables D.0 for general I/O (completely overrides any other I/O)

- TXENO: TX enable  $\rightarrow$  Disables D.1 for general I/O (completely overrides any other I/O)

- UCSZ02: see next slides

### **Control register: UCSROC**

#### 19.10.4 UCSRnC – USART Control and Status Register n C

| Bit           | 7       | 6       | 5     | 4     | 3     | 2      | 1      | 0      | _      |

|---------------|---------|---------|-------|-------|-------|--------|--------|--------|--------|

|               | UMSELn1 | UMSELn0 | UPMn1 | UPMn0 | USBSn | UCSZn1 | UCSZn0 | UCPOLn | UCSRnC |

| Read/Write    | R/W     | R/W     | R/W   | R/W   | R/W   | R/W    | R/W    | R/W    |        |

| Initial Value | 0       | 0       | 0     | 0     | 0     | 1      | 1      | 0      |        |

#### Bits 7:6 – UMSELn1:0 USART Mode Select

These bits select the mode of operation of the USARTn as shown in Table 19-4.

Table 19-4. UMSELn Bits Settings

| UMSELn1 | UMSELn0 | Mode                              |

|---------|---------|-----------------------------------|

| 0       | 0       | Asynchronous USART                |

| 0 1     |         | Synchronous USART                 |

| 1       | 0       | (Reserved)                        |

| 1       | 1       | Master SPI (MSPIM) <sup>(1)</sup> |

## Control register: UCSROC

#### Table 19-5. UPMn Bits Settings

| UPMn1 | UPMn0 | Parity Mode          |

|-------|-------|----------------------|

| 0     | 0     | Disabled             |

| 0     | 1     | Reserved             |

| 1     | 0     | Enabled, Even Parity |

| 1     | 1     | Enabled, Odd Parity  |

#### Table 19-6. USBS Bit Settings

| USBSn | Stop Bit(s) |

|-------|-------------|

| 0     | 1-bit       |

| 1     | 2-bit       |

#### Table 19-7. UCSZn Bits Settings

|   | UCSZn2 | UCSZn1 | UCSZn0 | Character Size |  |  |  |  |

|---|--------|--------|--------|----------------|--|--|--|--|

|   | 0      | 0      | 0      | 5-bit          |  |  |  |  |

|   | 0      | 0      | 1      | 6-bit          |  |  |  |  |

|   | 0      | 1      | 0      | 7-bit          |  |  |  |  |

| 4 | 0      | 1      | 1      | 8-bit          |  |  |  |  |

|   | 1      | 0      | 0      | Reserved       |  |  |  |  |

|   | 1      | 0      | 1      | Reserved       |  |  |  |  |

|   | 1      | 1      | 0      | Reserved       |  |  |  |  |

|   | 1      | 1      | 1      | 9-bit          |  |  |  |  |

#### Default: Frames of 10 bits.

#### Table 19-8. UCPOLn Bit Settings

| UCPOLn | Transmitted Data Changed (Output of TxDn Pin) | Received Data Sampled (Input on RxDn Pin) |

|--------|-----------------------------------------------|-------------------------------------------|

| 0      | Rising XCKn Edge                              | Falling XCKn Edge                         |

| 1      | Falling XCKn Edge                             | Rising XCKn Edge                          |

#### Initialization

```

#define F_CPU 1600000UL

#define BAUD 9600

#define MYUBRR F_CPU/16/BAUD-1

int main()

1

...

UART_Init(MYUBRR);

...

/* Function Body */

void UART_Init(unsigned int ubrr)

٦

UBRROH = (unsigned char) (ubrr>>8);

UBRROL = (unsigned char) ubrr;

UCSROB = (1 << RXENO) | (1 << TXENO);

```

# Transmission (19.6.1 datasheet & uart.c)

\*/

int uart\_putchar(char c, FILE \*stream)

```

/* Alarm (Beep, Bell) */ if (c == '\a')

```

```

fputs("*ring*\n", stderr);

return 0;

```

/\* Newline is translated into a Carriage Return \*/

if (c == '\n') {uart\_putchar('\r', stream); return 0;}

```

/* In uart.c: loop_until_bit_is_set(UCSROA, UDREO); */

while ( !(UCSROA & (1<<UDREO)) );

UDRO = c;</pre>

```

```

/* avr/io.h implements useful macros besides defining

* names for bit positions, registers like DDx (or do we

* use DDRx?) etc.

```

```

return 0;

```

ł

# Receiving

- int uart\_getchar(FILE \*stream) in uart.c is a simple line-editor that allows to delete and re-edit the characters entered, until either CR or NL is entered

- printable characters entered will be echoed using uart\_putchar()

- So you can see the character received by the MCU and you can verify whether the transmission was without error if you recognize the character as the transmitted one (as pressed by the keyboard)

- The core part in uart\_getchar is

```

int uart_getchar(FILE *stream)

{

...

while ( !(UCSROA & (1<<RXCO)) ) ;

c = UDRO;

...

uart_putchar(c, stream);

...

}</pre>

```

### ASCII Table

| De | ec  | Hx Oct | Cha | r                        | Dec | Hx | Oct | Html                  | Chr   | Dec | Hx | Oct | Html              | Chr | Dec | Hx | Oct | Html Cl           | hr  |

|----|-----|--------|-----|--------------------------|-----|----|-----|-----------------------|-------|-----|----|-----|-------------------|-----|-----|----|-----|-------------------|-----|

|    | D   | 0 000  | NUL | (null)                   | 32  | 20 | 040 | <b>⊛#</b> 32;         | Space | 64  | 40 | 100 | «#64;             | 0   | 96  | 60 | 140 | <b>«#96;</b>      | 100 |

|    | 1   | 1 001  | SOH | (start of heading)       | 33  | 21 | 041 | <b>∉#</b> 33;         | 1     | 65  | 41 | 101 | <b>A</b>          | A   | 97  | 61 | 141 | <b></b> ∉#97;     | a   |

|    | 2   | 2 002  | STX | (start of text)          | 34  | 22 | 042 | <b></b> <i>‱#</i> 34; | "     | 66  | 42 | 102 | <b>B</b>          | В   | 98  | 62 | 142 | <b>&amp;</b> #98; | b   |

| :  | 3   | 3 003  | ETX | (end of text)            | 35  | 23 | 043 | <b></b> ∉#35;         | #     | 67  | 43 | 103 | C                 | С   | 99  | 63 | 143 | <b>«#99;</b>      | С   |

|    | 4   | 4 004  | EOT | (end of transmission)    |     |    |     | <b>∝#</b> 36;         |       |     |    |     | <b>D</b>          |     |     |    |     | d                 |     |

|    | 5   | 5 005  | ENQ | (enquiry)                |     |    |     | <b></b> ∉37;          |       |     |    |     | <b>E</b>          |     |     |    |     | e                 |     |

|    | 6   |        |     | (acknowledge)            |     |    |     | <b>&amp;#</b> 38;     |       |     |    |     | <b></b> ∉70;      |     |     |    |     | <b>f</b>          |     |

|    | 7   | 7 007  | BEL | (bell)                   |     |    |     | <b></b> ∉39;          |       | 71  |    |     | G                 |     |     |    |     | «#103;            |     |

| -  | 8   | 8 010  |     | (backspace)              |     |    |     | <b>∝#40;</b>          |       | 72  |    |     | H                 |     |     |    |     | «#104;            |     |

| 1  | 9   | 9 011  |     | (horizontal tab)         |     |    |     | )                     |       | 73  |    |     | «#73;             |     |     |    |     | i                 |     |

| 10 | -   | A 012  |     | (NL line feed, new line) |     |    |     | *                     |       |     |    |     | «#74;             |     |     |    |     | j                 |     |

| 1. |     | B 013  |     | (vertical tab)           |     |    |     | +                     | +     |     |    |     | «#75;             |     |     |    |     | k                 |     |

| 1: |     | C 014  |     | (NP form feed, new page) |     |    |     | «#44;                 | 1.    |     |    |     | «#76;             |     |     |    |     | l                 |     |

| 1: |     | D 015  |     | (carriage return)        |     |    |     | -                     |       |     |    |     | M                 |     |     |    |     | m                 |     |

| 1. |     | E 016  |     | (shift out)              |     |    |     | .                     |       |     |    |     | <b>&amp;</b> #78; |     |     |    |     | n                 |     |

| 1. |     | F 017  |     | (shift in)               |     |    |     | ¢#47;                 |       |     |    |     | <b>∝#79;</b>      |     |     |    |     | o                 |     |

|    |     | .0 020 |     | (data link escape)       |     |    |     | «#48;                 |       |     |    |     | <b></b> ≪#80;     |     |     |    |     | p                 |     |

|    |     | .1 021 |     | (device control 1)       |     |    |     | «#49;                 |       |     |    |     | <b></b> ∉81;      |     |     |    |     | q                 |     |

|    |     |        |     | (device control 2)       |     |    |     | <b>2</b>              |       |     |    |     | <b></b> ∉82;      |     | I   |    |     | r                 |     |

|    |     |        |     | (device control 3)       |     |    |     | 3                     |       |     |    |     | ¢#83;             |     |     |    |     | s                 |     |

|    |     |        |     | (device control 4)       |     |    |     | <b>&amp;</b> #52;     |       |     |    |     | «#84;             |     |     |    |     | t                 |     |

|    |     |        |     | (negative acknowledge)   |     |    |     | <b>≪#53;</b>          |       |     |    |     | <b>U</b>          |     |     |    |     | u                 |     |

|    |     |        |     | (synchronous idle)       |     |    |     | «#54;                 |       |     |    |     | <b>V</b>          |     |     |    |     | v                 |     |

|    |     | .7 027 |     | (end of trans. block)    |     |    |     | <b>≪#55;</b>          |       |     |    |     | ¢#87;             |     |     |    |     | w<br>""           |     |

|    |     |        |     | (cancel)                 |     |    |     | <b>≪#56;</b>          |       |     |    |     | <b>X</b>          |     | I   |    |     | x                 |     |

|    |     | .9 031 |     | (end of medium)          |     |    |     | <b>≪#57;</b>          |       | 89  |    |     | <b>Y</b>          |     |     |    |     | y                 |     |

|    |     | A 032  |     | (substitute)             |     |    |     | <b>≪#58;</b>          |       |     |    |     | <b>≪#90;</b>      |     |     |    |     | z                 |     |

|    |     | B 033  |     | (escape)                 |     |    |     | «#59;                 |       |     |    |     | [                 | -   |     |    |     | {                 |     |

|    |     | .C 034 |     | (file separator)         |     |    |     | «#6O;                 |       |     |    |     | & <b>#</b> 92;    |     |     |    |     |                   |     |

|    |     | .D 035 |     | (group separator)        |     |    |     | l;                   |       |     |    |     | ]                 | -   |     |    |     | }                 |     |

|    |     | E 036  |     | (record separator)       |     |    |     | >                     |       |     |    |     | «#94;             |     |     |    |     | ~                 |     |

| 3. | 1 ] | F 037  | US  | (unit separator)         | 63  | ЗF | 077 | <b></b> ∉63;          | Z     | 95  | 5F | 137 | _<br>-            | -   | 127 | 7F | 177 | <b>∝#127;</b>     | DEP |

Source: www.LookupTables.com

#### Using vart.c

```

#include "uart.h"

. . .

FILE uart_str = FDEV_SETUP_STREAM(uart_putchar, uart_getchar, _FDEV_SETUP_RW);

...

int main(void)

{

// Initialize UART

uart_init();

stdout = stdin = stderr = &uart_str; // Set File outputs to point to UART stream

. . . .

// Can use fprintf and fscanf anywhere: here or in subroutines

. . .

return 0;

```